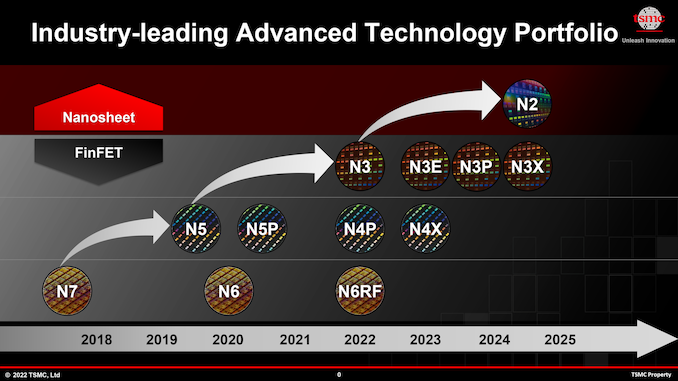

На своем технологическом симпозиуме 2022 года TSMC официально представила свою технологию производства N2 (класс 2 нм), которая должна быть запущена в производство в 2025 году и станет первым узлом TSMC, в котором будут использоваться полевые транзисторы со сквозным затвором (GAAFET). . Новый узел позволит разработчикам чипов значительно снизить энергопотребление своих продуктов, но улучшения скорости и плотности транзисторов кажутся значительно менее ощутимыми.

N2 от TSMC — это совершенно новая платформа, которая широко использует литографию EUV и представляет GAAFET (которые TSMC называет транзисторами с нанолистами), а также подачу питания на заднюю сторону. Новая транзисторная структура с затвором обещает широко известные преимущества, такие как значительно сниженный ток утечки (теперь, когда затворы расположены вокруг всех четырех сторон канала), а также возможность регулировать ширину канала для повышения производительности или снижения энергопотребления. . Что касается задней шины питания, она, как правило, предназначена для обеспечения лучшей подачи питания на транзисторы, предлагая решение проблемы увеличения сопротивления в задней части линии (BEOL). Планируется, что новая подача питания повысит производительность транзисторов и снизит энергопотребление.

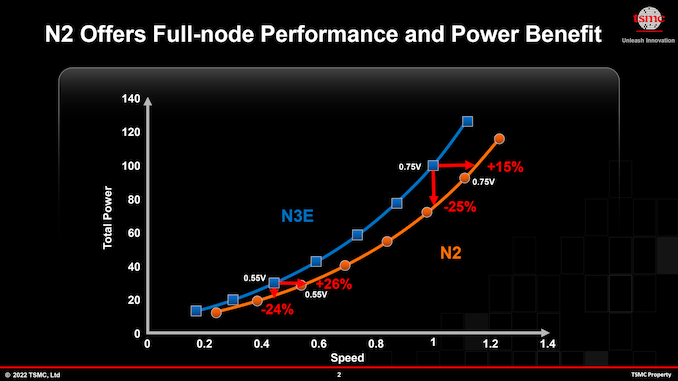

С точки зрения набора функций N2 от TSMC выглядит очень многообещающей технологией. Что касается реальных цифр, TSMC обещает, что N2 позволит разработчикам чипов повысить производительность на 10–15 % при той же мощности и количестве транзисторов или снизить энергопотребление при той же частоте и сложности на 25–30 %. увеличение плотности чипа более чем в 1,1 раза по сравнению с узлом N3E.

| Рекламируемые PPA улучшения новых технологических процессов Данные оглашаются во время телеконференций, мероприятий, пресс-брифингов и пресс-релизов |

|||||

| ТСМС | |||||

| N5 против N7 |

N3 против N5 |

N3E против N5 |

N2 против N3E |

||

| Сила | -30% | -25-30% | -34% | -25-30% | |

| Производительность | +15% | +10-15% | +18% | +10-15% | |

| Плотность стружки* | ? | ? | ~1,3X | >1,1X | |

| Объем Производство |

2 кв. 2022 г. | 2 полугодие 2022 г. | Q2/Q3 2023 | 2 полугодие 2025 г. | |

* Плотность чипов, опубликованная TSMC, отражает «смешанную» плотность чипов, состоящую из 50 % логических, 30 % SRAM и 20 % аналоговых.

По сравнению с N3E, повышение производительности и снижение энергопотребления, обеспечиваемые узлом TSMC N2, соответствуют тому, что обычно привносят новые узлы литейного производства. Но так называемые улучшения плотности микросхем (которые должны отражать прирост плотности транзисторов) составляют немногим более 10%. , что не особо вдохновляет, особенно если учесть, что N3E уже предлагает несколько меньшую плотность транзисторов по сравнению с ванильным N3. Принимая во внимание, что в наши дни SRAM и аналоговые схемы почти не масштабируются, в наши дни, вероятно, следует ожидать посредственных улучшений в плотности транзисторов реальных чипов. Тем не менее, увеличение плотности чипов на 10% примерно за три года, безусловно, не является хорошей новостью для графических процессоров и других чипов, которые живут или умирают в зависимости от быстрого увеличения количества транзисторов.

Принимая во внимание, что к тому времени, когда TSMC N2 начнет производство, компания также будет иметь узел N3S с оптимизированной плотностью, похоже, что литейный завод будет иметь две технологии обработки, основанные на разных типах транзисторов, но предлагающие очень одинаковую плотность транзисторов. никогда раньше не было.

Как обычно, TSMC предложит свой узел N2 с различными функциями и регуляторами, чтобы позволить разработчикам микросхем оптимизировать такие вещи, как мобильные и высокопроизводительные вычислительные устройства (обратите внимание, что TSMC называет HPC всем, что не является мобильным, автомобильным или специализированным, что включает в себя все, от от маломощного процессора ноутбука до высокопроизводительного вычислительного графического процессора, предназначенного для суперкомпьютеров). Кроме того, предлагаемые платформы включают в себя то, что TSMC называет «интеграцией микросхем», что, вероятно, означает, что TSMC позволяет своим клиентам легко интегрировать микросхемы N2 в пакеты с несколькими микросхемами, созданные с использованием различных узлов. Поскольку масштабирование плотности транзисторов замедляется, а использование новых технологических процессов становится все более дорогим, в ближайшие годы корпуса с несколькими микросхемами станут более распространенными, поскольку разработчики будут использовать их для оптимизации своих конструкций и затрат.

TSMC рассчитывает начать рискованное производство чипов с использованием своего производственного процесса N2 иногда во второй половине 2024 года, а это означает, что технология должна быть доступна для крупносерийного производства (HVM) коммерческих продуктов во второй половине 2025 года. Но, учитывая длиннее современных циклов производства полупроводников, вероятно, более прагматично ожидать, что первые чипы N2 станут доступны либо в самом конце 2025, либо в 2026 году, если все пойдет по плану.