В настоящее время большинство высокопроизводительных процессоров являются монолитными, но методологии проектирования медленно, но верно переходят к многочиплетным модулям по мере того, как передовые технологии производства становятся более дорогими в использовании. Ожидается, что в ближайшие годы многочиплетные системы в корпусах (SiP) получат гораздо более широкое распространение, а передовые технологии упаковки микросхем в 2,5D и 3D будут приобретать все большее значение. Чтобы ускорить и упростить разработку 3D-проектов, на этой неделе TSMC создала альянс 3DFabric Alliance.

Хотя многочиплетные SiP обещают упростить разработку и проверку очень сложных конструкций, они требуют совершенно новых методологий разработки, поскольку 3D-пакеты ставят ряд новых задач. Это включает в себя новые процессы проектирования, необходимые для интеграции 3D, новые методы подачи энергии, новые технологии компоновки и новые методы тестирования. Чтобы наилучшим образом использовать преимущества технологий упаковки 2.5D и 3D от TSMC (InFO, CoWoS и SoIC), индустрии разработки чипов нужна вся экосистема для совместной работы над упаковкой чиплетов — и именно для этого и создан 3DFabric Alliance. делать.

«Трехмерное стекирование кремния и передовые технологии компоновки открывают дверь в новую эру инноваций на уровне микросхем и систем, а также требуют обширного сотрудничества в экосистеме, чтобы помочь разработчикам найти лучший путь среди множества доступных им вариантов и подходов», — сказал он. Доктор Л.С. Лу, научный сотрудник TSMC и вице-президент по дизайну и технологической платформе.

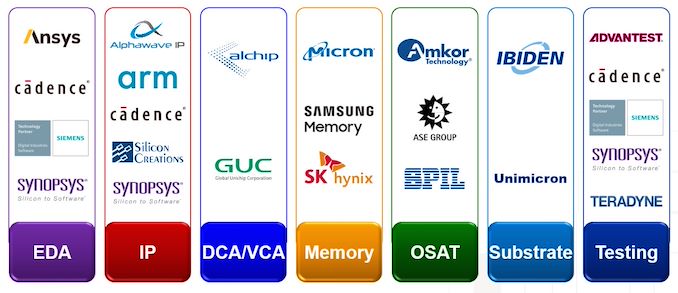

Альянс 3DFabric TSMC объединяет разработчиков средств автоматизации проектирования электроники (EDA), поставщиков интеллектуальной собственности, контрактных разработчиков микросхем, производителей памяти, производителей передовых подложек, компаний по сборке и тестированию полупроводников, а также групп, производящих оборудование, используемое для тестирования и проверки. В настоящее время в альянсе 19 членов, но ожидается, что со временем он будет расширяться по мере присоединения к группе новых членов.

Как лидер Альянса, TSMC установит определенные основные правила и стандарты. Тем временем члены 3DFabric Alliance будут совместно определять и разрабатывать некоторые спецификации для технологий 3DFabric TSMC, получат ранний доступ к дорожной карте и спецификациям TSMC 3DFabric, чтобы согласовать свои планы с планами литейного завода, а также с планами других членов альянса. , и сможет разрабатывать и оптимизировать решения, совместимые с новыми методами упаковки.

В конечном счете, TSMC хочет гарантировать, что члены 3DFabric Alliance будут предлагать своим клиентам совместимые и интероперабельные решения, которые позволят быстро разрабатывать и проверять мультичиплетные SiP, использующие 2.5D и 3D корпус.

Например, чтобы унифицировать экосистему проектирования с помощью квалифицированных инструментов и потоков EDA, TSMC разработала свой стандарт 3Dblox. 3Dblox охватывает различные аспекты создания мультичиплетных устройств с использованием методологий компоновки 2.5D и 3D (таких как определения микросхем и интерфейсов), включая физическую реализацию, энергопотребление, рассеивание тепла, электромиграционное ИК-падение (EMIR) и временную/физическую проверку. .

«Благодаря коллективному лидерству TSMC и наших партнеров по экосистеме наш альянс 3DFabric предлагает клиентам простой и гибкий способ раскрыть возможности 3D IC в своих проектах, и нам не терпится увидеть инновации, которые они могут создать с помощью наших технологий 3DFabric. “, – добавил Лу.

В конечном счете, TSMC предполагает, что альянс значительно упростит и оптимизирует процесс разработки более совершенных чипов, особенно для малых и средних компаний, которые в большей степени полагаются на сторонние IP/проекты. Например, если компания хочет разработать SiP, состоящий из логических микросхем, сложенных вместе и подключенных к подсистеме памяти на основе HBM3, программное обеспечение EDA от Ansys Cadence, Synopsys и Siemens позволит ей разработать совместимые микросхемы, поставщики IP будут продавать эти микросхемы. блоков, которых у дизайнера еще нет, TSMC будет производить кремний, производители памяти предложат совместимые HBM3 KGSD (известно хорошие стековые кристаллы), а затем Ase Technology соберет все вместе. В то же время компании, у которых нет собственных инженеров, смогут заказать дизайн всего SiP (или отдельных чипсетов) через Alchip или GUC, а затем со временем обновлять свой продукт, если это необходимо, без необходимости перепроектировать все, поскольку SiP будет построен в соответствии со стандартами 3DFabric и 3Dblox.

В настоящее время 3Dblox поддерживается четырьмя основными разработчиками EDA. В конце концов, он будет поддержан всеми членами альянса, если это необходимо.

В то время как крупные компании, такие как AMD и Nvidia, как правило, разрабатывают свои собственные технологии IP, межсетевого взаимодействия и компоновки, мультичиплетные SiP обещают сделать разработку сложных чиплетных процессоров доступной для небольших компаний. Для них стандартная сторонняя интеллектуальная собственность, быстрое время выхода на рынок и правильная интеграция являются ключом к успеху, поэтому 3DFabric Alliance и то, что он дает, будет для них жизненно важным.

Источник: TSMC