Компания Synopsys объявила, что ее инструменты проектирования и интеллектуальная собственность (ИС) готовы к использованию. Samsung 2-нм техпроцесс литейного производства.

Samsung недавно объявила, что будет готова к массовому производству 2-нм полупроводниковых чипов в следующем году и что этот процесс будет усовершенствован в 2027 году.

Инструменты проектирования Synopsys сертифицированы для Samsung 2-нм техпроцесс Foundry GAA

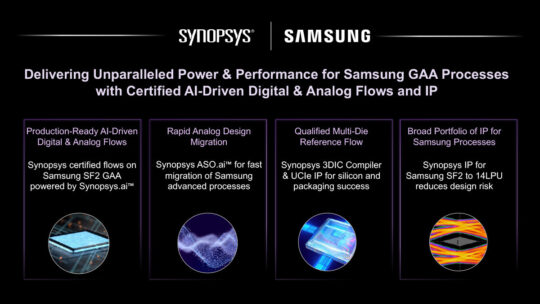

Фирмы, занимающиеся разработкой микросхем, и клиенты, заинтересованные в производстве своих микросхем с использованием Samsung 2-нм процесс Foundry будет рад узнать, что аналоговые и цифровые инструменты Synopsys, управляемые искусственным интеллектом, получили сертификацию для этого технологического узла с несколькими выводами микросхем.

Synopsys.ai — это полнофункциональный пакет автоматизации проектирования электроники (EDA), который улучшает миграцию аналоговых проектов, PPA и производительность для Samsung 2-нм технологический узел Gate Allaround (GAA) компании Foundry. Решение Synopsys для совместной оптимизации технологий проектирования на основе искусственного интеллекта (DTCO) оптимизировало Samsung2-нм техпроцесс, улучшающий площадь, производительность и энергоэффективность.

Инструмент Synopsys DSO.ai используется для повышения производительности проектирования и оптимизации PPA, а Synopsys ASO.ai — для ускорения миграции аналоговых проектов. Эти процессы были применены для миграции проектов с архитектуры FinFET на архитектуру GAA, что означает, что клиенты могут перенести свои конструкции микросхем, используемые для 8-нм (или более старого) процесса FinFET, на новый 2-нм процесс GAA.

Производители чипов могут использовать инструменты Synopsys для разработки новых методов проектирования чипов, включая обратную маршрутизацию питания, методологию учета эффектов локальной компоновки и проектирование ячеек из нанолистов, для повышения эффективности и производительности процесса SF2. Samsung Технологический узел Foundry SF2Z может еще больше повысить производительность, мощность и занимаемую площадь (на 20%).

История продолжается после нашего видео ниже, в котором сравнивается производительность Exynos 2400 с производительностью Snapdragon 8 поколение 3.

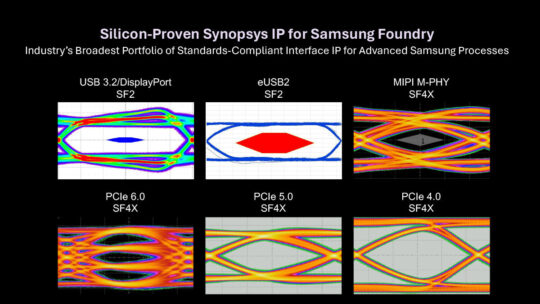

Synopsys UCIe IP использовался для записи микросхем с использованием процессов SF2 и SF4x для более быстрой интеграции чиплетов в корпуса с несколькими кристаллами. Задержка, мощность и соединение между кристаллами также были улучшены в процессе SF5A. Компилятор 3DIC компании Synopsys можно использовать для гетерогенной интеграции 2,5D и 3D, а также для расширенной упаковки.

Более того, компания Synopsys сообщила, что то же решение DTCO будет использоваться для оптимизации Samsung 1,4-нм технологический узел Foundry (SF1.4).