TSMC объявила о своем новаторском 1,6-нм производственном процессе для чипов, а также включает в себя внутреннюю сеть подачи питания, которая еще больше повышает энергоэффективность и плотность транзисторов.

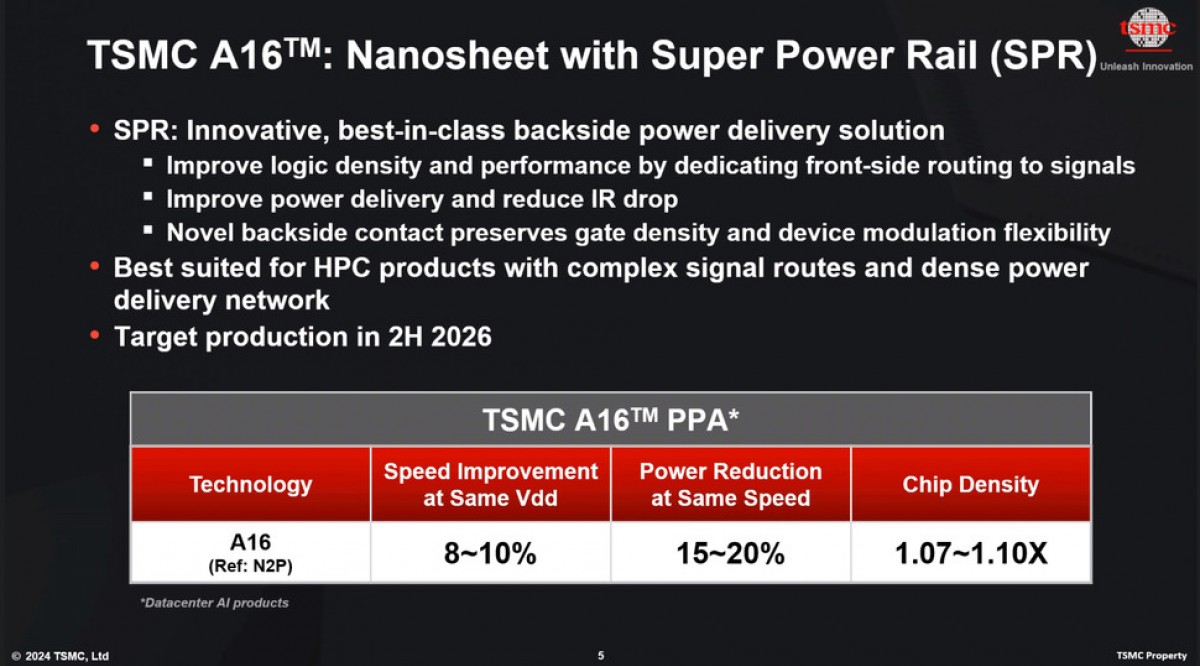

Анонсированный 1,6-нм техпроцесс основан на нанолистовых транзисторах с полным затвором, как и будущие архитектуры N2, N2P и N2X, основанные на 2-нм узле. Один только новый процесс позволяет увеличить тактовую частоту на 10% при том же напряжении и снизить энергопотребление до 20% при той же частоте и сложности. В зависимости от конструкции чипа новый 1,6-нм техпроцесс может вместить до 10 % больше транзисторов.

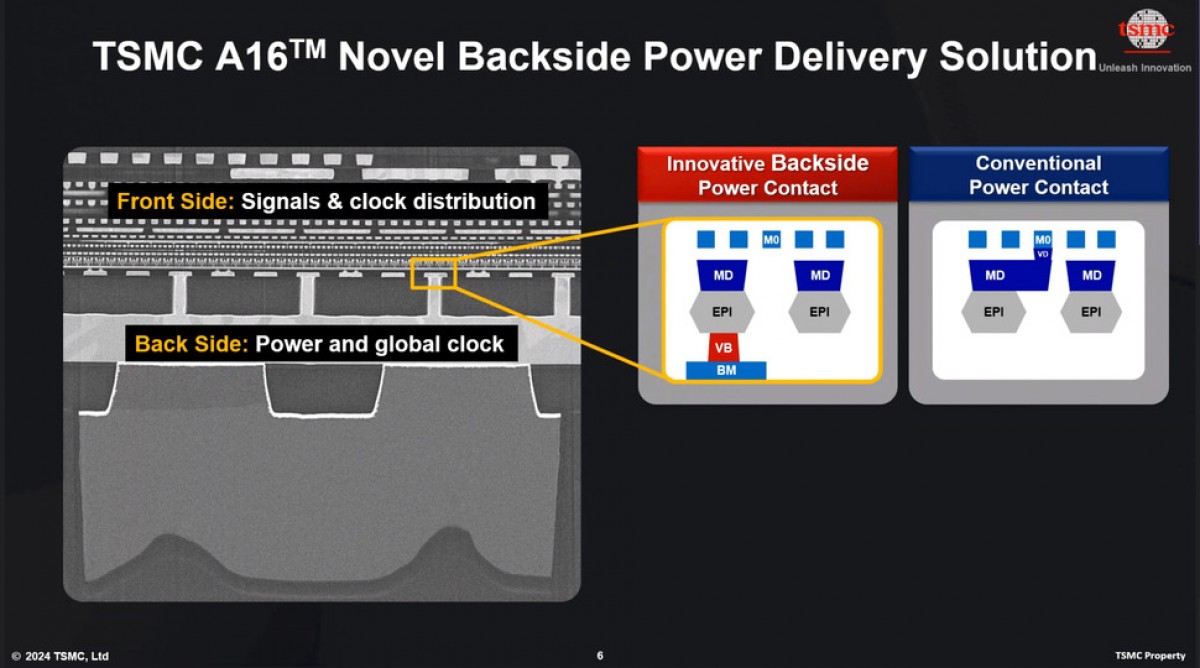

Задняя сеть подачи питания, возможно, является еще более впечатляющим аспектом этих будущих чипов, поскольку она позволяет увеличить плотность транзисторов и улучшить подачу энергии, что, в свою очередь, влияет на производительность. TSMC заявляет, что наряду с Super Power Rail (SPR), типом вилки, используемой для подключения чипа к источнику питания, задняя сеть подачи питания окажется полезной в основном для процессоров AI и HPC, которым требуется сложная сигнальная проводка и плотная электросети.

Сроки производства запланированы на вторую половину 2026 года, если все пойдет по плану, а первые готовые к использованию продукты будут отправлены в 2017 году.