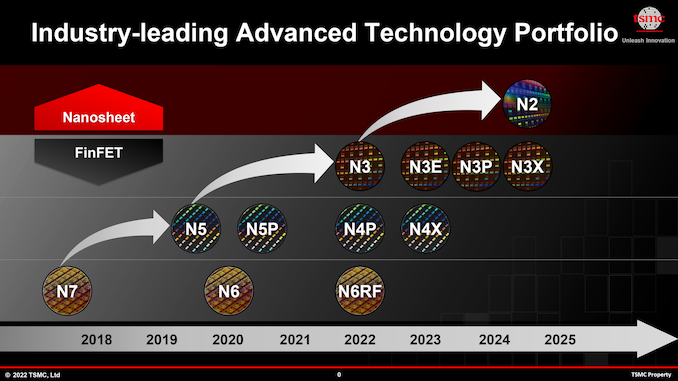

Когда TSMC первоначально представила свой техпроцесс N2 (класс 2 нм) в начале этого месяца, компания рассказала, как новый узел будет построен на основе двух новых передовых производственных технологий: транзисторов со сквозным затвором и шин питания на задней стороне. . Но, как мы узнали из симпозиума ЕС на прошлой неделе, планы TSMC немного более тонкие, чем было объявлено вначале. В отличие от некоторых своих конкурентов, TSMC не будет внедрять обе технологии в начальной версии своего узла N2. Вместо этого в первой итерации N2 будут реализованы только транзисторы с универсальным затвором, а подача питания на заднюю сторону будет поставляться с более поздней версией узла.

До сих пор TSMC упомянула две отличительные особенности N2: транзисторы с нанолистовым затвором (GAA) и задние силовые шины. Транзисторы GAA имеют два уникальных преимущества перед FinFET: они решают многие проблемы, связанные с током утечки, поскольку каналы GAAFET горизонтальны и со всех четырех сторон окружены затворами. Между тем, задняя шина питания позволила улучшить подачу питания на транзисторы, что повышает производительность и снижает энергопотребление.

Но, как выясняется, TSMC не планирует начинать с нанолистовых GAA-транзисторов и задних шин питания в начальном поколении своего техпроцесса N2. Как сообщила компания на прошлой неделе на своем симпозиуме в ЕС, в первом поколении N2 будут использоваться только транзисторы с универсальным затвором. С другой стороны, подача питания на задней стороне появится позже с более продвинутыми реализациями N2.

На данный момент компания не слишком много говорила о том, почему они не внедряют обратную подачу питания как часть своего первоначального узла N2. Но, обсуждая раздвоение, TSMC отметила, что подача питания на задней стороне в конечном итоге добавит дополнительные этапы процесса, которых компания, по-видимому, старается избежать при первой попытке с GAAFET.

Отсутствие обратной подачи питания в исходной версии технологии изготовления N2, возможно, объясняет довольно умеренное улучшение производительности N2 по сравнению с узлом N3E.. В то время как для высокопроизводительных вычислений (ЦП, ускорители и т. д.) повышение производительности на 10–15 % при той же мощности и сложности не кажется впечатляющим, падение мощности на 25–30 % при той же скорости и сложности кажется быть очень хорошим для мобильных приложений.

| Рекламируемые PPA улучшения новых технологических процессов Данные оглашаются во время телеконференций, мероприятий, пресс-брифингов и пресс-релизов |

|||||

| ТСМС | |||||

| N5 против N7 |

N3 против N5 |

N3E против N5 |

N2 против N3E |

||

| Сила | -30% | -25-30% | -34% | -25-30% | |

| Производительность | +15% | +10-15% | +18% | +10-15% | |

| Плотность стружки* | ? | ? | ~1,3X | >1,1X | |

| Объем Производство |

2 кв. 2022 г. | 2 полугодие 2022 г. | Q2/Q3 2023 | 2 полугодие 2025 г. | |

* Плотность чипов, опубликованная TSMC, отражает «смешанную» плотность чипов, состоящую из 50 % логических, 30 % SRAM и 20 % аналоговых.

Учитывая, что TSMC всегда предлагает несколько версий своих узлов, то, что у TSMC есть несколько вариантов, запланированных для N2, не так уж удивительно. Тем не менее, немного странно видеть, что TSMC проделала довольно долгий путь к обратной подаче энергии.

По сравнению с конкурентами это в конечном итоге станет заметным отличием от того, как конкурирующая Intel планирует реализовать свой собственный переход питания GAAFET / backside с помощью процесса Intel 20A. Intel намерена представить свои транзисторы GAA RibbonFET и межсоединения PowerVia вместе в середине 2024 года, дойдя до создания внутреннего псевдоузла только для того, чтобы сосредоточиться на разработке RibbonFET. TSMC, с другой стороны, использует более осторожный подход к рискам и инновациям, который потенциально заставляет TSMC двигаться медленнее, но также является подходом, который традиционно лучше подходит для потребности TSMC в предоставлении более стабильных и последовательных обновления своих потрясающих предложений.

И хотя у нас еще есть несколько лет, будет интересно посмотреть, что это означает для конкурентоспособности узла N2 TSMC первого поколения. Будет ли процесс GAAFET без обратной подачи энергии иметь существенные недостатки? Согласно текущим графикам, мы узнаем ответ на этот вопрос во второй половине 2025 года, когда планируется запустить первый узел TSMC N2 в крупносерийное производство (HVM).