Одна из тенденций в области высокопроизводительных вычислений (HPC), которая становится все более очевидной, заключается в том, что энергопотребление на чип и на единицу стойки не остановится с ограничениями воздушного охлаждения. Поскольку суперкомпьютеры и другие высокопроизводительные системы уже достигли, а в некоторых случаях и превзошли эти пределы, требования к мощности и плотность мощности продолжают расти. И, основываясь на новостях с недавнего ежегодного технологического симпозиума TSMC, мы должны ожидать продолжения этой тенденции, поскольку TSMC закладывает основу для еще более плотных конфигураций чипов.

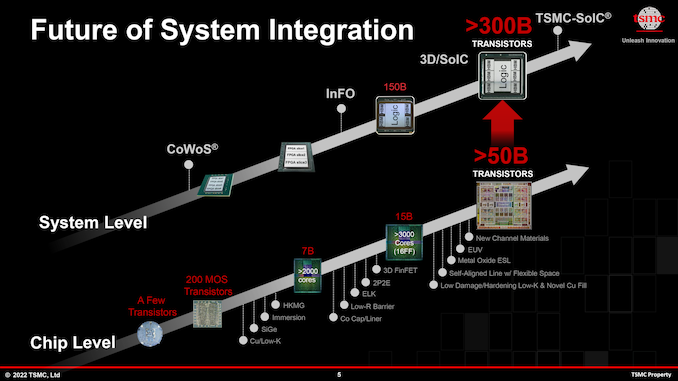

Проблема не нова: энергопотребление транзисторов уменьшается не так быстро, как размеры транзисторов. И поскольку производители чипов не собираются отказываться от производительности (и не могут обеспечить полугодовой прирост для своих клиентов), в области высокопроизводительных вычислений мощность на транзистор быстро растет. В качестве дополнительной проблемы чиплеты прокладывают путь к созданию чипов с еще большим количеством кремния, чем традиционные пределы сетки, что хорошо для производительности и задержки, но еще более проблематично для охлаждения.

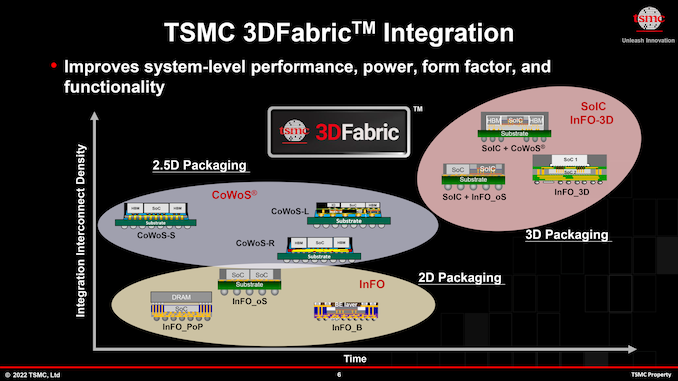

Обеспечением такого рода кремния и роста мощности стали современные технологии, такие как TSMC’a CoWoS и InFO, которые позволяют производителям микросхем создавать интегрированные многочиплетные системы в корпусах (SiP) с удвоением количества кремния, которое в противном случае разрешено TSMC. пределы сетки. К 2024 году усовершенствования технологии упаковки TSMC CoWoS позволят создавать еще более крупные мультичиплетные SiP, при этом TSMC планирует сшить вместе до четырех чиплетов размером с сетку. TSMC и ее партнеры смотрят на) и производительность, но, естественно, за счет огромного энергопотребления и тепловыделения.

Уже сейчас флагманские продукты, такие как ускорительный модуль NVIDIA H100, требуют мощности свыше 700 Вт для обеспечения максимальной производительности. Таким образом, перспектива использования нескольких чипсетов размером с GH100 в одном продукте вызывает недоумение — и бюджеты на электроэнергию. TSMC предполагает, что через несколько лет появятся многочиплетные SiP с энергопотреблением около 1000 Вт или даже выше, что создаст проблему охлаждения.

При 700 Вт H100 уже требует жидкостного охлаждения; и история почти такая же для Ponte Vecchio на базе чипсета от Intel и Instinct MI250X от AMD. Но даже традиционное жидкостное охлаждение имеет свои пределы. TSMC предполагает, что к тому времени, когда совокупная мощность процессоров достигнет 1 кВт, в центрах обработки данных потребуется использовать иммерсионные системы жидкостного охлаждения для таких экстремальных процессоров искусственного интеллекта и высокопроизводительных вычислений. Иммерсионное жидкостное охлаждение, в свою очередь, потребует перепроектирования самих центров обработки данных, что станет серьезным изменением конструкции и серьезной проблемой непрерывности.

Помимо краткосрочных проблем, как только центры обработки данных будут настроены на иммерсионное жидкостное охлаждение, они будут готовы к еще более горячим чипам. Жидкостное иммерсионное охлаждение обладает большим потенциалом для работы с большими охлаждающими нагрузками, и это одна из причин, по которой Intel вкладывает значительные средства в эту технологию, пытаясь сделать ее более популярной.

Помимо иммерсионного жидкостного охлаждения, есть еще одна технология, которая может использоваться для охлаждения сверхгорячих чипов — водяное охлаждение на кристалле. В прошлом году TSMC сообщила, что экспериментировала с водяным охлаждением на кристалле, и заявила, что с помощью этой технологии можно охлаждать даже SiP мощностью 2,6 кВт. Но, конечно же, встроенное водяное охлаждение само по себе является чрезвычайно дорогой технологией, которая приведет к беспрецедентному уровню затрат на эти экстремальные решения для ИИ и высокопроизводительных вычислений.

Тем не менее, хотя будущее не высечено в камне, кажется, что оно отлито в кремнии. У клиентов TSMC, производящих чипы, есть клиенты, готовые платить большие деньги за эти сверхвысокопроизводительные решения (вспомните операторов гипермасштабируемых облачных центров обработки данных), даже с учетом высоких затрат и технической сложности, которые влекут за собой это. Чтобы вернуть все к тому, с чего мы начали, вот почему TSMC в первую очередь разрабатывает процессы упаковки CoWoS и InFO — потому что есть клиенты, готовые и стремящиеся выйти за пределы сетки с помощью технологии чиплетов. Мы уже наблюдаем некоторые из них сегодня с такими продуктами, как массивный процессор Cerebras Wafer Scale Engine, и с помощью больших чипсетов TSMC готовится сделать более мелкие (но все же ломающие сетку) конструкции более доступными для своей более широкой клиентской базы.

Такие экстремальные требования к производительности, компоновке и охлаждению не только вынуждают производителей полупроводников, серверов и систем охлаждения работать на пределе своих возможностей, но и требуют модификации облачных центров обработки данных. Если массивные SiP для рабочих нагрузок ИИ и высокопроизводительных вычислений действительно получат широкое распространение, облачные центры обработки данных в ближайшие годы будут совершенно другими.