[ad_1]

Наряду с некоторыми новыми объявлениями о планах по 2-нм технологическому узлу, компания TSMC также представила обновленную информацию о прогрессе и дорожной карте для своих технологических процессов семейства N3 на сегодняшнем Североамериканском технологическом симпозиуме 2023. Последнее поколение технологических узлов TSMC на базе FinFET, семейство N3, как ожидается, будет существовать в той или иной форме еще много лет в качестве самого плотного узла, доступного для клиентов, которым не нужен более современный процесс на базе GAAFET.

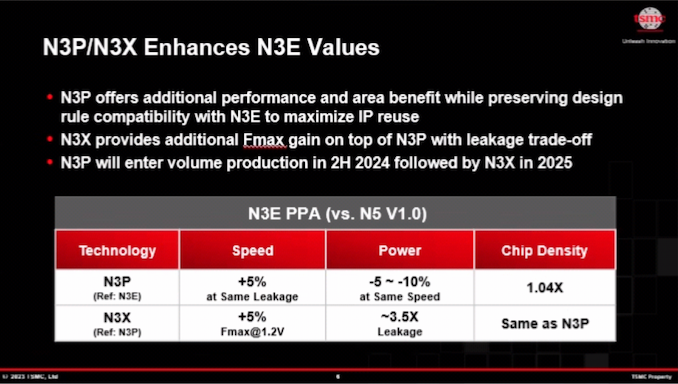

Крупные обновления дорожной карты N3 от TSMC касались N3P и его высокопроизводительного варианта N3X. Как объявила сегодня компания TSMC, N3P будет оптическим уменьшением N3E, предлагая повышенную производительность, сниженное энергопотребление и увеличенную плотность транзисторов по сравнению с N3E, при этом сохраняя совместимость с правилами проектирования N3E. Между тем, N3X будет отличаться экстремальной производительностью при плотности 3 нм класса, предлагая более высокую тактовую частоту для высокопроизводительных CPU и других процессоров.

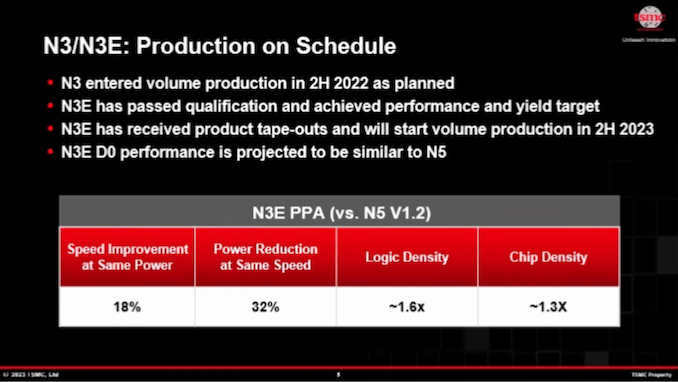

N3E: 3 нм для всех идет по графику

Вкратце напомним, что семейство технологических процессов N3 (3-нм класса) компании TSMC состоит из нескольких вариантов, включая базовый N3 (он же N3B), расслабленный N3E со сниженной стоимостью, N3P с повышенной производительностью и плотностью чипов, а также N3X с более высокими допусками по напряжению. В прошлом году компания также говорила о N3S с максимальной плотностью транзисторов, но в этом году компания продолжает хранить молчание об этом узле, и он нигде не упоминается в ее слайдах.

Ванильный узел N3 компании TSMC имеет до 25 EUV-слоев, причем TSMC использует EUV-двойной паттернинг на некоторых из них, чтобы обеспечить более высокую плотность транзисторов логики и SRAM по сравнению с N5. EUV-шаги являются дорогостоящими в целом, а EUV с двойным рисунком еще больше увеличивает эти расходы, поэтому ожидается, что этот процесс производства будет использоваться только горсткой клиентов, которые не так обеспокоены требуемыми большими расходами.

| Рекламируемый PPA Совершенствование новых технологических технологий Данные, объявленные во время конференц-звонков, мероприятий, пресс-брифингов и пресс-релизов |

|||

| TSMC | |||

| N3 vs N5 |

N3E против N5 |

||

| Питание | -25-30% | -32% | |

| Производительность | +10-15% | +18% | |

| Область логики

Сокращение* % Плотность логики* |

0.58x

-42% 1.7x |

0.625x

-37.5% 1.6x |

|

| Размер ячейки SRAM | 0,0199 мкм² (-5% по сравнению с N5) | 0,021 мкм² (такой же, как N5) | |

| Том Производство |

Конец 2022 года | H2 2023 | |

Ожидается, что большинство клиентов TSMC, заинтересованных в технологическом процессе класса 3 нм, будут использовать расслабленный узел N3E, который, по данным TSMC, идет по графику и достигает целевых показателей производительности. N3E использует до 19 слоев EUV и совсем не полагается на двойное вытравливание EUV, что снижает сложность и затраты. Компромиссом является то, что N3E предлагает более низкую плотность логики, чем N3, и имеет тот же размер ячеек SRAM, что и нода N5 компании TSMC, что делает ее несколько менее привлекательной для тех клиентов, которые стремятся к увеличению плотности/площади. В целом, N3E обещает более широкое технологическое окно и более высокую производительность, что является двумя важнейшими показателями при производстве микросхем.

“N3E будет лучше, чем N3, с точки зрения выхода продукции, сложности технологического процесса, что напрямую отражается в [wider] технологическое окно”, – сказал Кевин Чжан, вице-президент по развитию бизнеса в TSMC.

N3P: более высокая производительность, более высокая плотность транзисторов

После N3E компания TSMC продолжит оптимизацию плотности транзисторов семейства N3 с помощью N3P, который будет основан на N3E, предлагая улучшенные характеристики транзисторов. Усовершенствованный технологический узел позволит разработчикам чипов либо увеличить производительность на 5% при тех же утечках, либо снизить мощность на 5% ~ 10% при тех же тактовых частотах. Новый узел также увеличит плотность транзисторов на 4% для “смешанного” дизайна чипа, который TSMC определяет как чип, состоящий из 50% логики, 30% SRAM и 20% аналоговых схем.

В рамках обсуждения N3P компания TSMC подчеркнула, что улучшение плотности было достигнуто за счет корректировки оптических характеристик своих сканеров. Поэтому вполне вероятно, что TSMC сможет уменьшить все типов структур микросхем, что сделает N3P привлекательным узлом для конструкций с интенсивным использованием SRAM.

“N3P – это повышение производительности, она на 5% выше, по крайней мере, на 5% выше, чем N3E, – объясняет Чжан. Он также имеет 2% оптическую усадку, которая доводит плотность транзисторов до 1,04x”.

| Рекламируемые PPA Усовершенствования новых технологических технологий Данные, объявленные во время конференц-звонков, мероприятий, пресс-брифингов и пресс-релизов |

|||||

| TSMC | |||||

| N3 vs N5 |

N3E против N5 |

N3P vs N4E |

N3X vs N3P |

||

| Питание | -25-30% | -32% | -5% ~ 10% | выше | |

| Производительность | +10-15% | +18% | +5% | +5% Fmax @ 1,2 В |

|

| Плотность микросхем | ? | ? | |||

| Размер ячейки SRAM | 0,0199 мкм² (-5% по сравнению с N5) | 0,021 мкм² (то же, что и N5) | ? | ? | |

| Том Производство |

Конец 2022 года | H2 2023 | H2 2024 | 2025 | |

Поскольку N3P является оптическим уменьшением N3E, в нем будут сохранены правила проектирования N3E, что позволит разработчикам чипов быстро повторно использовать ИС N3E на новом узле. Следовательно, N3P также прогнозируется как один из самых популярных узлов N3 компании TSMC, поэтому ожидайте, что такие компании, как Cadence и Synopsys, предложат разнообразные ИС для этой технологической технологии, получая преимущества прямой совместимости с существующими N3E в процессе разработки. TSMC утверждает, что N3P будет готов к производству во второй половине 2024 года.

N3X: максимальная производительность и плотность

Наконец, для разработчиков высокопроизводительных вычислительных приложений, таких как CPU и GPU, TSMC уже несколько последних поколений предлагает семейство X высоковольтных узлов, ориентированных на производительность. Как было объявлено на прошлогоднем мероприятии, семейство N3 получит свой собственный X-вариант с метким названием N3X.

По сравнению с N3E, N3X, как ожидается, предложит как минимум на 5% более высокую тактовую частоту по сравнению с N3P. Это достигается за счет того, что узел более терпим к более высоким напряжениям, что позволяет разработчикам чипов увеличивать тактовые частоты в обмен на более высокую общую утечку.

TSMC утверждает, что N3X будет поддерживать напряжения (по крайней мере) 1,2 В, что является довольно экстремальным напряжением для производственного процесса 3 нм класса. Стоимость утечки, в свою очередь, значительна: TSMC прогнозирует 250% увеличение утечки мощности по сравнению с более сбалансированным узлом N3P. Это подчеркивает, почему N3X действительно пригоден только для процессоров класса HPC, и что разработчикам микросхем придется проявлять повышенную осторожность, чтобы держать свои самые мощные (и энергоемкие) чипы под контролем.

Что касается плотности транзисторов, N3X будет предлагать ту же плотность, что и N3P. TSMC не прокомментировала, будет ли она также поддерживать совместимость правил проектирования с N3P и N3E, поэтому будет интересно посмотреть, что в итоге произойдет.

Последний узел семейства N3 в текущей дорожной карте TSMC, компания утверждает, что N3X будет готов к производству в 2025 году.

[ad_2]